Informe-5 8255 Fun

UNIVERSIDAD DE LAS FUERZAS ARMADAS ESPE DEPARTAMENTO DE ELÉCTRICA Y ELECTRÓNICA Microprocesadores CONSULTA No. 1 SEGUND

Views 59 Downloads 0 File size 2MB

Recommend stories

- Author / Uploaded

- Santiago David

Citation preview

UNIVERSIDAD DE LAS FUERZAS ARMADAS ESPE DEPARTAMENTO DE ELÉCTRICA Y ELECTRÓNICA

Microprocesadores CONSULTA No. 1 SEGUNDO PARCIAL

TEMA: Funcionamiento del PPI 8255 (Interfaz Periférica Programable)

NRC: 3193

Docente: Ing. Miroslava Aracely Zapata Rodríguez

Nombre: Villavicencio Freddy

Sangolquí, 12 de Diciembre del 2018

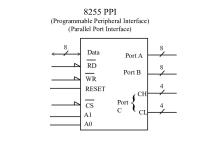

1. Tema: Funcionamiento del PPI 8255 (Interfaz Periférica Programable) 2. Objetivos 2.1 Objetivo general: Conocer el funcionamiento y operación del PPI 8255 (Interfaz Periférica Programable) 2.2 Objetivos específicos: Conocer las aplicaciones del periférico programable de E/S y su compatibilidad con los diferentes tipos de microprocesadores Intel. Realizar la simulación de un ejemplo mediante el cual se pueda observar los modos de operación del 8255A. Reconocer la distribución de pines del CI y sus conexiones. 3. Marco teórico El PPI 8255 El circuito PPI (Interfaz Periférica Programable) 8255A de Intel es un dispositivo programable de entrada/salida de propósito general diseñado para ser usado con microprocesadores Intel. El PPI es un circuito integrado de 40 terminales, de las cuales 24 son de entrada/salida y se pueden programar individualmente en 2 grupos de 12 y se puede utilizar en 3 diferentes modos de operación. Contiene 3 puertos programables paralelos de 8 bits. Cada puerto tiene un registro. Tiene también un registro de control de los puertos.

Figura 1: Modelo a bloques del PPI 8255.

Estructura interna del PPI 8255

Figura 2: Estructura interna del PPI 8255.

Distribución de terminales del 8255.

Figura 3: Distribución de terminales del 8255.

Tabla de verdad de operación del PPI 8255.

Tabla 1: Tabla de verdad de operación del PPI 8255.

Periférico programable 8255 Descripción funcional: Básicamente se trata de tres puertos (A,B,C) de ocho bits, encontrándose el puerto C dividido en dos puertos de cuatro bits. Estos cuatro puertos formados (dos de ocho bits y dos de cuatro) se organizan en dos grupos de 12 bits. Cada grupo contiene un puerto de ocho bits y otro de cuatro.

El grupo A está formado por el puerto A y los 4 bits más significativos del puerto C. Grupo A: PA0...PA7 + PC4...PC7 El grupo B está constituido por el puerto B junto a los 4 bits menos significativos del puerto C. Grupo B: PB0…PB7 + PC0...PC3

El puerto C está especialmente diseñado para ser dividido en dos mitades y servir de apoyo a los puertos A y B en algunos sistemas. Programación: El 8255 soporta 3 modos de operación:

Modo 0 (entrada y salida básica). Modo 1 (entrada y salida con señales de control). Modo 2 (bus bidireccional de comunicaciones).

El modo para el puerto A y B se puede seleccionar por separado; el puerto C está dividido en dos mitades relacionadas con el puerto A y el B. Tabla 2: Direccionamiento.

Figura 4: Formato de la definición del modo.

Figura 5: Formato para activar/desactivar un bit del puerto C.

Características del 8255 operado en modo 0

Se le asigna operaciones de entrada y salida a cada uno de los tres puertos. No se usa un protocolo (handshaking) para el intercambio de los datos. Los datos simplemente se escriben o leen de un puerto específico.

Definición funcional básica del modo 0

Se tiene 2 puertos de 8 bits y 2 de 4 bits. Cualquier puerto puede ser entrada o salida. Las salidas tienen LATCH (cerrojo). Las entradas no tienen LATCH. Hay 16 posibles configuraciones de entrada/salida en este modo.

Figura 6: Diagrama de bloques funcionales en modo 0.

Ciclo de máquina de Entrada/Salida del Z80

Figura 7: Ciclo de máquina de Entrada/Salida del Z80.

Características del 8255 operado en modo 1 (Strobed Input/Output) La transferencia de datos de E/S hacia o de puertos específicos se realiza con señales de control o de Handshaking. Es un modo de transferencia concertada. Definición funcional básica del modo 1

El puerto A y el puerto B usan líneas del puerto C para generar o aceptar señales de handshaking en modo de pulsos (strobes). Características: Se tienen 2 grupos (grupos A y B) Cada grupo contiene 8 bits de puerto de datos y 4 bits de puerto de control/datos. Cada puerto de datos de 8 bits puede usarse como estrada o como salida independientemente. Tanto las entradas como las salidas de latchean. El puerto de 4 bits se usa para control y status del puerto de datos de 8 bits.

Figura 8: Operación del 8255 en modo 1.

Señales de Control cuando el Puerto (A o B) está definido como Entrada

Figura 9: Señales de Control cuando el Puerto (A o B) está definido como Entrada.

STB (Strobe Input): Un nivel bajo en esta entrada, carga los datos en el latch de entrada. IBF (Input Buffer Full F/F): Un nivel alto en esta salida indica que el dato ya fue cargado en el latch de entrada. IBF se pone en alto por un nivel bajo en STB y se pone en bajo debido al flanco positivo de la entrada RD. INTR (Pedido de Interrupción): Un nivel alto en esta salida se puede usar para interrumpir al 𝑢P. INTR se pone en alto cuando STB está en 1, IBF está en 1 e INTR está en 1. Se pone en 0 con el flanco negativo de RD.

Figura 10: Operación en modo 1 cuando el Puerto (A o B) está definido como Entrada.

Características del 8255 operado en modo 2

Figura 11: El 8255 operado en modo 2.

El 8255 programado para operar en modo 2 hace bidireccional al puerto A y el puerto C proporciona las líneas de control de la transferencia

Figura 12: El 8255 operado en modo 2; solo como entrada y solo como salida.

Figura 13: Ejemplo de conexión del PPI con el Z80.

4. Desarrollo a) Ejemplo 1: Aplicación con LCDs Para esta aplicación se utiliza una memoria y LCDs para mostrar mensajes de activación según el puerto escogido, el diseño se conforma de los siguientes bloques: Bloque de activación del circuito: Para activar el circuito necesario diseñar un circuito de inicialización el cual permita resetear los contadores para que inicien la cuenta desde cero, y así evitar errores de visualización en el LCD. SW1 SW-SPDT

R5

D2

1k

1N4004 Reset

C5 1uF

Fig 14: Circuito de inicialización

A continuación se activa manualmente la señal de reloj con un pulsador conectado a un flipflop D, para grabar la activación (1) en la entrada del circuito que genera la señal de reloj, cuya señal a su vez activa los contadores y la entrada ENABLE del LCD permitiendo la visualización de caracteres.

D

R21

5

Q

1k CLK

U25

U27:A

4

R

74LS74

VCC

6

Q

1

R

8

3

CLK

2

S

4

U26:A

Q DC

1

7

TR

RV1 TH

1

LED-GREEN

10k

6

R22

1nF

C3

CLK2

D19

CV

GND

2

C4

2 7404

20%

5

3

555

330

100uF

Fig 15: Activación del cajero por medio de la señal de reloj

Bloque de contadores: En este bloque se genera el conteo de los contadores para acceder a las localidades de la memoria, cuando el conteo llega a 21 (10101). Se trunca los contadores por medio del buffer. Hasta resetear los contadores para activar otro puerto del 8255.

U29 D0 D1 D2 D3

1

3 4 5 6

2

CLK

7 10 2 9 1

3 Reset

14 13 12 11 15

Q0 Q1 Q2 Q3 RCO

ENP ENT CLK LOAD MR 74161

U30 3 4 5 6 7 10 2 9 1

D0 D1 D2 D3

14 13 12 11 15

Q0 Q1 Q2 Q3 RCO

ENP ENT CLK LOAD MR 74161

U34 2

1

4

3

NAND_5

Figura 16: Contadores.

Bloque de conexión 8255 y memoria: En la figura 15 se muestra la conexión de la memoria y el controlador de periféricos 8255, se conectan las 8 salidas de la memoria con las 8 entradas del bus de datos del 8255 U21 10 9 8 7 6 5 4 3 25 24 21 23 2 26 27 20 22 1

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14

U28 D0 D1 D2 D3 D4 D5 D6 D7

11 12 13 15 16 17 18 19

34 33 32 31 30 29 28 27

0

CLK2 A0 A1

5 36 9 8 35 6

D0 D1 D2 D3 D4 D5 D6 D7

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

RD WR A0 A1 RESET

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

CS

CE OE VPP

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

27C256

4 3 2 1 40 39 38 37 18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10

8255A

Figura 17: Conexión controlador-memoria.

Bloque de activación de puertos: Se conecta un LCD al puerto A y otro al puerto C del 8255, cuando se active alguno de los puertos se mostrara el mensaje “PUERTO ACTIVADO” en el LCD correspondiente. -

Activación puerto A:

Se activa el puerto C en modo lectura, con la siguiente combinación:

0 0

A0 A1

Figura 18: Combinación; puerto A salida de datos.

LCD1

D0 D1 D2 D3 D4 D5 D6 D7 7 8 9 10 11 12 13 14

RS RW E 4 5 6 CLK2

1 2 3

VSS VDD VEE

LM016L

U28 34 33 32 31 30 29 28 27

-

D0 D1 D2 D3 D4 D5 D6 D7

5 36 9 8 35

RD WR A0 A1 RESET

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

18 Figura PB0 19: Activación Puerto A modo lectura. 19

Activación puerto C: 6

4 3 2 1 40 39 38 37

U28 CS

PB1 PB2 PB3 PB4 PB5 PB6 PB7 PA0 PA1 PC0 PA2 PC1 PA3 PC2 PA4 PC3 PA5 PC4 PA6 PC5 PA7 PC6 PC7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

20 21 22 23 24 25 4 3 14 2 15 1 16 40 17 39 13 38 12 37 11 10 18 19 20 21 22 23 24 25

Se activa el puerto C en modo lectura, con la siguiente combinación: D0 D1 D2 D3 D4 D5 D6 D7

A1

Figura 20: Combinación; puerto C salida de datos. 14 15 16 17 13 12 11 10

LCD6 LM016L

VSS VDD VEE

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

CLK2

1 2 3

8255A

D0 D1 D2 D3 D4 D5 D6 D7

CS

A0

7 8 9 10 11 12 13 14

6

0 1

RS RW E

5 RD 36 WR 9 A0 8255A 8 A1 35 RESET

4 5 6

34 33 32 31 30 29 28 27

Figura 21: Activación Puerto C modo lectura.

Programación en memoria:

Figura 22: Programación en memoria.

b) Ejemplo 2: Aplicación con Display 7 segmentos y leds Para este ejemplo se utiliza el puerto A y el puerto C para lectura de datos, y el puerto B para escritura de datos. La salida de datos del puerto A será por medio de leds, y para el puerto B se utilizan Display 7 segmentos. U15 2 3 4 5 6 7 8 9

DSW3 16 15 14 13 12 11 10 9

OFF

ON

1 2 3 4 5 6 7 8

1 0 0 1 1 1 1 0

19 1

B0 B1 B2 B3 B4 B5 B6 B7

18 17 16 15 14 13 12 11

CE AB/BA 74LS245

DIPSW_8

U3 34 33 32 31 30 29 28 27

0 0

5 36 9 8 35

0 1

6

D0 D1 D2 D3 D4 D5 D6 D7

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

RD WR A0 A1 RESET

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

CS

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

0 0

4 3 2 1 40 39 38 37 18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10

1 0 0 1 1 0 0 1

1 0 0 1 1 1 1 0

A0 A1 A2 A3 A4 A5 A6 A7

U4 7 1 2 6 4 5 3

8255A

U1 2 3 4 5 6 7 8 9 19 1

A0 A1 A2 A3 A4 A5 A6 A7

B0 B1 B2 B3 B4 B5 B6 B7

18 17 16 15 14 13 12 11

CE AB/BA 74LS245

A B C D BI/RBO RBI LT

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

7448

U5 7 1 2 6 4 5 3

A B C D BI/RBO RBI LT

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

7448

Figura 23: Aplicación con display y LCD – circuito completo.

Uso del 74245: El CI 74245 es un transmisor/receptor octal diseñado para comunicaciones asincrónicas de dos vías entre buses de datos. La entrada de dirección DR controla la transmisión del bus A al bus B ó del bus B al bus A, dependiendo de su valor lógico. La entrada de habilitación (E’) sirve para aislar los buses Tabla 3: Tabla de verdad: 74245

Bloque de activación de puertos: -

Puerto A en modo lectura:

Se activa el puerto A en modo escritura, con la siguiente combinación:

0 0

A0 A1

Figura 24: Combinación; puerto A de escritura de datos. U15 2 3 4 5 6 7 8 9

1 1 0 0 1 0 0 1

19 1

A0 A1 A2 A3 A4 A5 A6 A7

B0 B1 B2 B3 B4 B5 B6 B7

18 17 16 15 14 13 12 11

CE AB/BA 74LS245

U3 34 33 32 31 30 29 28 27

-

5 36 9 8 35 6

D0 D1 D2 D3 D4 D5 D6 D7

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

RD WR A0 A1 RESET

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

4 3 2 1 40 39 38 37 18 19 20 21 22 23 24 25

Figura 25: Activación Puerto A modo lectura.

Puerto B en modo escritura: CS

Se activa el puerto B14en modo escritura, con la siguiente combinación: PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

15 16 17 13 12 11 10

8255A

0 1

U3 34 33 32 31 30 29 28 27

D0 D1 D2 D3 D4 D5 D6 D7

PA0

A0 A1

4

3 PA1 Combinación; puerto B de escritura de datos. Figura 26: 2 PA2 PA3 PA4 PA5 PA6 PA7

1 40

39 Se ingresan los datos por el puerto B: 38

RD WR A0 A1 RESET

6

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

CS

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

37 18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10

1 1 1 1 1 1 0 0

5 36 9 8 35

U4

Figura 27: escritura de datos por el puerto B.

7 1 2 6 4 5 3

En el bis de datos D se8255A puede visualizar los datos ingresados por el puerto B:

7448

DSW3

1 0 0 0 0 1 1 1

16 15 14 13 12 11 10 9

OFF

ON

A B C D BI/RBO RBI LT

1 2 3 4 5 6 7 8

0 0 1 1 1 1 1 1

DIPSW_8

U3 34 33 32 31 30 29 28 27

D0 D1 D2 D3 D4 D5 D6 D7

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

4 3 2 1 40 39 38 37

5 18 RD PB0 0Figura 28: Visualización 36 19 de datos D. WR por el busPB1 9 8 35

6

A0 A1 RESET CS

PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3

20 21 22 23 24 25

14 15 16 17

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

-

Puerto C en modo lectura:

En este puerto se conecta el transmisor/receptor seguido de dos decodificador 74LS247, que U3 permiten la visualización de los números BCD ingresados por el bus de datos D.

34 33 32 31 30 29 28 27

D0 D1 D2 D3 D4 D5 D6 D7

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

RD WR A0 A1 RESET

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

4 3 2 1 40 39 38 37

Se activa el puerto C en modo lectura, con la siguiente combinación:

CS

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

A0 A1

Figura 29: Combinación; puerto C salida de datos.

14 15 16 17 13 12 11 10

U4 7 1 2 6 4 5 3

8255A

U1 2 3 4 5 6 7 8 9 19 1

A0 A1 A2 A3 A4 A5 A6 A7

18 17 16 15 14 13 12 11

B0 B1 B2 B3 B4 B5 B6 B7

A B C D BI/RBO RBI LT

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

7448

U5 7 1 2 6 4 5 3

CE AB/BA 74LS245

A B C D BI/RBO RBI LT

QA QB QC QD QE QF QG

13 12 11 10 9 15 14

7448

Figura 30: Activación Puerto C modo lectura.

c) Ejemplo 3: Operación Lectura/Escritura DSW1 16 15 14 13 12 11 10 9

0 0 0 0 0 0 0 0

OFF

ON

1 2 3 4 5 6 7 8

0 0 0 0 0 0 0 0

DIPSW_8

U2 34 33 32 31 30 29 28 27

0 0 0 0 0 0

5 36 9 8 35 6

D0 D1 D2 D3 D4 D5 D6 D7

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

RD WR A0 A1 RESET

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

CS

PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

4 3 2 1 40 39 38 37

0 0 0 0 0 0 0 0

18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10

1 1 1 1 1 1 1 1

8255A

Figura 14: 8255 en operación entrada/salida.

0 0 0 0 0 0 0 0

6

0 1

18 19 20 21 22 23 24 25

1 0 0 1 1 0 0 1

5 36 9 8 35

5. Conclusiones

INTEL 8255 es una interfaz versátil que nos permite tener puertos de entrada y salida simple, así como puertos de E/S sincronizados. Por lo tanto dicha interfaz está diseñada para trabajar con casi cualquier microprocesador. Para poder manejar Interfaz Periférica Programable del 8255 es importante dominar el lenguaje ensamblador, para poder acoplar los diferentes tipos de microprocesadores compatibles con el mismo. La simulación planteada permitió conocer los modos de operación del PPI 8255, también se utilizó un CI 74LS245 (Buffer de 8 líneas) para controlar la transmisión de datos entre los buses.

6. Bibliografía - Gianoti, J. (2018). “Interfaz paralela PPI”. Disponible en: http://www.academia.edu/6604833/INTERFAZ_PARALELA_PPI - Thomas L. Floyd, (2006). “Fundamentos de sistemas digitales”. España, Madrid: Pearson. - Canto, C. (nd). “El PPI Intel 8255” Microprocesadores. Disponible en: http://galia.fc.uaslp.mx/~cantocar/microprocesadores/EL_Z80_PDF_S/16_PPI.PDF - Ferreira, J. (nd). “Controlador de Interfaz Paralelo Programable (PPI) 8255”. Disponible en: http://webapp.pucmm.edu.do/WebSISE/Estudiante/materias/201120122/SD-ITT-327T-001/ITT-327-T%20Unidad%20VI-1.%208255.pdf