Microprocesador 8255

UNIVERSIDAD DE LAS FUERZAS ARMADAS – ESPE. Departamento de Eléctrica y Electrónica. Microprocesadores TEMA: Consulta: C

Views 99 Downloads 2 File size 289KB

Recommend stories

- Author / Uploaded

- Raham Castillo

Citation preview

UNIVERSIDAD DE LAS FUERZAS ARMADAS – ESPE. Departamento de Eléctrica y Electrónica.

Microprocesadores TEMA: Consulta: Circuito Integrado 8255. Interfaz Periférica Programable

NRC: 2666 Nombre: Raham Castillo

Profesora: Miroslava Zapata

Fecha: 13 de Julio del 2018

1. Tema Consulta: Circuito Integrado 8255.

2. Descripción del 8255 El 8255A es un dispositivo de E / S programable de propósito general diseñado para transferir los datos de E / S para interrumpir E / S bajo ciertas condiciones, según sea necesario. Se puede usar con casi cualquier microprocesador. Consta de tres puertos de E / S bidireccionales de 8 bits (24 líneas de E / S) que se pueden configurar según el requisito.

3. Detalle de los Puertos 8255A tiene tres puertos, es decir, PUERTO A, PUERTO B y PUERTO C.

El puerto A contiene un latch / buffer de salida de 8 bits y un buffer de entrada de 8 bits. El puerto B es similar a PORT A. El puerto C se puede dividir en dos partes, es decir, PORT C inferior (PC0-PC3) y PORT C superior (PC7-PC4) por la palabra de control.

Estos tres puertos se dividen en dos grupos, es decir, el Grupo A incluye el PUERTO A y el PUERTO superior C. El Grupo B incluye PUERTO B y PUERTO inferior C. Estos dos grupos se pueden programar en tres modos diferentes, es decir, el primer modo se llama modo 0, el segundo modo se denomina modo 1 y el tercer modo se denomina modo 2.

4. Características del 8255 Las características destacadas de 8255A son las siguientes:

Se compone de 3 puertos IO de 8 bits, es decir, PA, PB y PC. El bus de direcciones / datos debe ser demultiplexado externamente. Es TTL compatible. Ha mejorado la capacidad de conducción de CC.

5. Arquitectura del 8255 La siguiente figura muestra la arquitectura de 8255.

Figura 1. Arquitectura del 8255

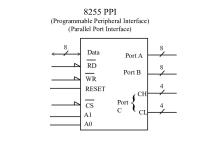

6. Diagrama de Pines D7-D0 RESET CS RD WR A0 y A1 PA7-PA0 PB7-PB0 PC7-PC0 Vcc GND

Figura 2. Distribución de Pines

7. Lógica de Control de lectura/escritura

Bus de direcciones Restablecer la entrada Chip select Leer la entrada Escribir la entrada Dirección de puerto Puerto A (BIT) Puerto B (BIT) Puerto C (BIT) 5 voltios 0 voltios

Este bloque es responsable de controlar la transferencia interna / externa de datos / control / palabra de estado. Acepta la entrada desde la dirección de la CPU y los buses de control, y a su vez emite comandos a ambos grupos de control. CS Significa Chip Select. A LOW en esta entrada selecciona el chip y habilita la comunicación entre el 8255A y la CPU. Está conectado a la dirección decodificada, y A0 y A1 están conectados a las líneas de dirección del microprocesador. Su resultado depende de las siguientes condiciones: CS 0 0 0 0

A1 0 0 1 1

A0 0 1 0 1

Resultado PUERTO A PUERTO B PUERTO C Registro de control

Tabla 1.Activación de los Puertos y registro de control

WR Significa escribir. Esta señal de control habilita la operación de escritura. Cuando esta señal baja, el microprocesador escribe en un puerto de E / S o registro de control seleccionado. REINICIAR Esta es una señal alta activa. Borra el registro de control y establece todos los puertos en el modo de entrada. RD Significa Read. Esta señal de control habilita la operación de lectura. Cuando la señal es baja, el microprocesador lee los datos del puerto de E / S seleccionado del 8255. A0 y A1 Estas señales de entrada funcionan con RD, WR y una de las señales de control. A continuación se muestra la tabla que muestra sus diversas señales con su resultado. A

1

A

0

RD

WR

CS

0

0

0

1

0

0

1

0

1

0

Resultado Operación de entrada PUERTO A → Bus de datos PUERTO B → Bus de datos

1

0

0

1

0

0

0

1

0

0

0 1 1

1 0 1

1 1 1

0 0 0

0 0 0

PUERTO C → Bus de datos Operación de salida Bus de datos Bus de datos Bus de datos Bus de Datos

→ → → →

PUERTO PUERTO PUERTO PUERTO

A A B D

Tabla 2. Modo de escritura

8. Modos de Funcionamiento 8255A tiene tres modos de funcionamiento diferentes:

Modo 0 : en este modo, el puerto A y B se utilizan como dos puertos de 8 bits y el puerto C como dos puertos de 4 bits. Cada puerto se puede programar en modo de entrada o modo de salida donde las salidas están enclavadas y las entradas no están

enganchadas. Los puertos no tienen capacidad de interrupción. Modo 1 : en este modo, el puerto A y B se utilizan como puertos de E / S de 8 bits. Se pueden configurar como puertos de entrada o salida. Cada puerto usa tres líneas del puerto C como señales de apretón de manos. Las entradas y salidas están

cerradas. Modo 2 : en este modo, el puerto A puede configurarse como el puerto bidireccional y el puerto B, ya sea en el modo 0 o en el modo 1. El puerto A utiliza cinco señales del puerto C como señales de saludo para la transferencia de datos. Las tres señales restantes del Puerto C se pueden usar como E / S simple o como protocolo de enlace para el puerto B.

Figura 3. Modos de funcionamiento