Catedra Interface a Perifericos 8255 PPI

MICROPROCESADORES I ELECTRONICA DIGITAL III INTERFASE PROGRAMABLE A PERIFERICOS PPI 8255 INTRODUCCIÓN Este integrado de

Views 79 Downloads 107 File size 145KB

Recommend stories

- Author / Uploaded

- Mauricio

Citation preview

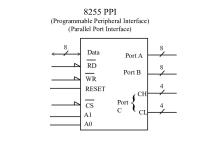

MICROPROCESADORES I ELECTRONICA DIGITAL III INTERFASE PROGRAMABLE A PERIFERICOS PPI 8255 INTRODUCCIÓN Este integrado de la firma INTEL, conocido como PPI 8255 (Programmable Peripherical Interfase) realizado con tecnología LSI, fue diseñado como interfase entre el bus de datos paralelo de los microprocesadores 8080, 8085, aunque puede ser utilizado por otros tales como el 8086 u 8088. Tiene la virtud de poder configurarse, con distintos modos de funcionamiento, por software a través del bus de datos, lo cual le brinda una gran flexibilidad. El dispositivo dispone de 24 terminales de entrada/salida, que pueden ser programados en dos grupos de 12 y brindar al usuario 3 modos básicos de operación. Dichos terminales trabajan con niveles TTL. Permite también poner en "1" o en "0" un único bit de una de las puertas. La capacidad de corriente es de 1mA, lo que permite mediante el uso de apropiados transistores, el manejo de circuitos de potencia.

DESCRIPCIÓN GENERAL. El 8255 PPI contiene: -Dos puertas (A y B) de 8 bits que pueden trabajar, según se programen, como puertas de entrada/salida de datos en paralelo. -Una puerta (puerta C) de 8 bits que pueden trabajar como dos puertos independientes de 4 bits cada uno, como líneas independientes, o como señales de control para los puertos A y B. -Un registro de control para la programación de los puertos, que no es otra cosa que la selección de los modos de funcionamiento para las puertas. La figura 1 muestra la configuración interna y las líneas de control de la PPI.

1

Figura 1

SEÑALES HACIA EL MICROPROCESADOR Mediante las líneas A0 A1 se direccionan las tres puertas y el registro de control. La línea RD es la señal de lectura para la puerta direccionada y la línea WR es la señal de escritura para escribir en alguno de las tres puertas o en el registro de control. La línea CS (Chip selec) permite la habilitación del dispositivo. La tabla 1 resume las operaciones básicas de lectura y escritura de la PPI, realizadas por la CPU.

2

A1

A0

RD

WR

CS

Operación de entrada (lectura)

0

0

0

1

0

Puerta A -> Bus de Datos

0

1

0

1

0

Puerta B -> Bus de Datos

1

0

0

1

0

Puerta C -> Bus de Datos Operación de salida (escritura)

0

0

1

0

0

Bus de Datos -> Puerta A

0

1

1

0

0

Bus de Datos -> Puerta B

1

0

1

0

0

Bus de Datos -> Puerta C

1

1

1

0

0

Registro de Control Inactivo

X

X

X

X

1

Bus de Datos 3 state

1

1

0

1

0

Condición Ilegal

X

X

1

1

0

Bus de Datos 3 state Tabla 1

CONTROL GRUPO A Y GRUPO B. La configuración funcional de cada puerta es programada por el software del sistema. En esencia el micro procesador escribe una palabra de control hacia el 8255, la cual define la "forma de operación" del sistema de entrada/salida (I/O). Cada uno de los bloques de control (grupo A y B) aceptan comandos desde la lógica de control de lectura/escritura. Los grupos A y B se definen como: Grupo A: Puerta A y parte alta de la puerta C Grupo B: Puerta B y parte baja de la puerta C El registro de control es un registro de escritura, es decir, no se puede realizar la lectura de este registro.

PUERTAS A, B Y C. El 8255 PPI tiene tres puertas de 8 bits cada una. Todas pueden ser configuradas de distintas formas, tanto como entradas o como salidas. Puerta A: un latch o buffer/latch de 8 bits como salida, un buffer o un buffer/latch de 8 bits entrada.

3

Puerta B: un latch de 8 bits como salida, un buffer o un buffer/latch de entrada. Puerta C: un latch de salida de 8 bits y un buffer de entrada de 8 bits. Esta puerta puede ser dividida en dos puertas de 4 bits, de acuerdo con el modo de operación del grupo. Cada una de éstas partes podrán ser usadas para transferir datos o como líneas de control para las puertas A y B.

DESCRIPCIÓN DE LOS MODOS DE OPERACIÓN. Selección de modos Hay tres modos básicos de operación que pueden ser seleccionados de acuerdo a la programación del dispositivo, estos son: Modo 0 --Modo 1 --Modo 2 ---

I/O básica I/O strobed (Modo de reconocimiento mutuo, Handshaking) Bidireccional

Los modos para las puertas A y B pueden ser definidos en forma separada, mientras que la puerta C está dividida en dos partes de 4 bits y cada una de estas partes pueden ser utilizadas como entradas o salidas en forma independiente. No siempre se se dispone de las cuatro líneas de cada grupo, esto depende del modo en que trabaja la puerta A o B , como se describirá luego. Para indicarle a la PPI cual es el modo de operación elegido, se debe escribir la palabra de control apropiada, lo cual se logra "escribiendo" en el registro direccionado por la condición A1 y A0 en "1" (ver tabla 1). La palabra de control mencionada tiene el siguiente formato:

4

CARACTERÍSTICAS DE FUNCIONAMIENTO EN MODO BIT SET/RESET. Cualquiera de los ocho bits del puerto C puede ser puesto en "1" o "0" mediante una simple instrucción de salida, esto reduce los requerimientos de soft-ware en aplicaciones de control. En otras palabras, este modo permite a la CPU tener capacidad de direccionar un bit de la puerta C para la operación de escritura. Puede ser usado cuando la puerta C está como salida o cuando el puerto C está siendo usado como status/control de las puertas A o B.

5

La palabra de control para este formato se muestra a continuación:

Conviene aclarar que el bit direccionado por D1, D2 y D3 es puesto en "1" o en "0" de acuerdo al bit D0.

MODOS DE OPERACIÓN. MODO 0. (MODO BÁSICO DE ENTRADA/SALIDA) Esta configuración provee operaciones simples de entrada o salida de datos, no utiliza líneas de control con el periférico, es decir, todas las señales son de transferencia de datos y todos los bits de las puertas A y B se definen como entradas o como salidas. Las partes alta y baja de la puerta C en este modo de operación, pueden trabajar independientemente como entrada o como salida según se la haya definido en la palabra de control. Resumiendo: En el modo 0 se dispone de 2 puertas de 8 bits y dos de 4 bits. Cuando es entrada se comporta como buffer y para salida como latch. MODO 1. (HANDSHAKING DE ENTRADA/SALIDA). Handshaking implica un modo de reconocimiento mutuo, es decir que existe un cierto protocolo de comunicación entre el periférico y la PPI. En este formato se provee la forma de transferir datos desde o hacia una puerta especificada en conjunto con líneas de strobe o handshaking. Para funcionar en este modo, las puertas A o B utilizan algunas líneas de la puerta C para generar o recibir estas líneas de protocolo o handshaking.

6

Las puertas A y B son utilizadas como puertas unidireccionales de entrada o de salida y algunas líneas de la puerta C, como líneas de control. En este modo, cada puerta (A o B), utilizan 3 líneas de la puerta C, quedando de esta puerta dos líneas libres, las que se pueden utilizar como en el modo 0 para entrada o salida. Estas dos líneas (PC6-PC7 o PC5-PC4) se utilizan como líneas de control para la puerta A cuando trabaja en modo 2. Los puertos A y B, tanto de entrada como de salida, capturan los datos, es decir tienen un latch. Las líneas de la puerta C que son ocupadas como líneas de control varían según la puerta A o B, trabaje como entrada o salida. Puertos A y B en modo 1 como entradas. Las señales de control son: STB: Habilitación de entrada. Un "0" en esta señal de entrada carga los datos provenientes del periférico en el latch de entrada de la PPI. La línea PC4 es la señal STB para el puerto A y la línea PC2 para el puerto B. IBF: (Input Buffer Full) Buffer de entrada lleno. Un "1" en esta salida indica que el dato ha sido cargado en el latch de entrada. Es la respuesta a una señal STB, es decir, cuando el periférico escribe un dato en el latch de la puerta correspondiente mediante la señal STB, la PPI responde poniendo en "1" la línea IBF que le indica al periférico que ha tomado el dato escrito por este último y también le indica que no envíe un nuevo dato hasta que IBF pase a nivel "0", lo cual se produce cuando la CPU lee la puerta correspondiente. La línea PC5 es la encargada de generar esta línea para la puerta A y la línea PC1 para la puerta C. INTR: Pedido de interrupción. Señal de salida que en "1" pide interrupción a la CPU. La salida INTR se coloca en "1" con el flanco positivo de STB si IBF está en "1" e INTE está en 1, INTE es una habilitación interna de interrupción que puede ser puesta en "1" o "0" mediante una operación de escritura en el formato bit set/reset, esta operación se describirá luego. La línea INTR vuelve a nivel "0" en el flaco negativo de la señal de lectura RD. La línea PC3 genera esta señal para el puerto A y la línea PC0 lo hace para el puerto B. La figura 2 ilustra el funcionamiento de estas líneas.

7

Figura 2

La figura 3 muestra un enlace entre un puerto A o B de la PPI con un periférico y el diagrama de tiempos de las líneas de control.

Figura 3 Activando STB (STB=0) por un periférico exterior, se carga el dato enviado en la puerta correspondiente y el 8255 genera la señal de reconocimiento IBF=1. Cuando se desactiva STB (STB=1), el 8255 genera INTR, si está activado por software el bit de habilitación de interrupciones INTE, y la CPU contesta el pedido de interrupción leyendo el

8

dato en el puerto mediante la línea RD. Una vez realizada esta operación, el 8255 desactiva IBF quedando en espera de un nuevo dato. Puertos A y B en modo 1 como salidas. Al igual que en el funcionamiento como entrada, algunas de las líneas del puerto C, se utilizan como señales de protocolo para la comunicación entre la PPI y el periférico. Las líneas de control utilizadas se detallan a continuación: OBF: (Output Buffer Full) Buffer de salida lleno. Señal de salida mediante la cual la PPI le indica al periférico que tiene un dato para enviarle. Esta señal se activa, es decir toma el valor "0", con el flanco positivo de la señal de escritura WR y pasa a nivel "1" con el flanco negativo de la señal de entrada ACK. Las líneas PC7 y PC1 se encargan de generar OBF para los puertos A y B respectivamente. ACK: (Acknowledge) Reconocimiento de entrada. Esta señal es generada por el periférico, un "0" en esta señal de entrada del 8255 le informa que el dato en la puerta correspondiente ha sido aceptado. En esencia es una línea de reconocimiento por parte del periférico indicando que ha tomado el dato puesto en la salida del puerto y que está dispuesto para recibir uno nuevo. Las líneas PC6 y PC2 se encargan de esta entrada para los puertos A y B respectivamente. INTR: Pedido de interrupción. Un "1" en esta salida puede ser usado para interrumpir a la CPU cuando un dispositivo ha aceptado el dato enviado, indicándole que transmita un nuevo dato. La señal INTR toma el valor "1" cuando se produce un flanco positivo de la señal ACK si OBF está en "1" y la habilitación interna INTE está también en "1". Para pasar INTR a "0" la CPU debe escribir un nuevo dato, es decir que INTR pasa a "0" con el flanco negativo de WR. Las líneas PC3 y PC0 se encargan de esta señal para los puertos A y B. La figura 4 ilustra el funcionamiento de estas líneas.

9

Figura 4 La figura 5 ilustra un enlace entre un puerto de la PPI y un periférico que recibe datos de la CPU a través de la PPI.

Figura 5

Cuando la CPU escribe un dato en alguno de los puertos A o B de la PPI, se activa la señal OBF indicándole al periférico que tiene un dato para enviarle. Este último contestará

10

generando una señal de reconocimiento que ingresará a la PPI por la línea ACK, indicándole a la que tomó el dato enviado. Finalizado lo anterior, el 8255 desactiva OBF y genera la señal INTR (si está permitida) para indicarle a la CPU que escriba un nuevo dato en el puerto. En algunas aplicaciones puede intercalarse a la salida de la PPI un buffer tri-state si la comunicación se realiza mediante un BUS por el cual circulan datos procedentes de distintos periféricos. Dicho buffer deberá permanecer en alta impedancia en tanto el periférico no genere la señal de reconocimiento.

Palabra de Estado. Haciendo una lectura del puerto C cuando los puertos A y B están trabajando en el modo 1, se puede obtener el estado de las puertas A y B. Solo hay que tener en cuenta la forma en que están trabajando las puertas A y B, ya sea como entrada o como salida. La figura 6 muestra la disposición de los bits de estado.

Figura 6

Habilitación de Interrupciones. Para el control de las señales INTRA e INTRB, se han de activar los bits de habilitación INTEA e INTEB de la puerta C usando el modo bit set/reset. El registro de control, bajo formato bit-set/reset del puerto C, se programa para activar los bits PC4 = INTEA y PC2 = INTEB. La figura 7 muestra un ejemplo de programación, con el microprocesador 8080, de los puertos de la PPI y de los bits de habilitación de interrupciones.

11

Figura 7 MODO 2. Trabajar en modo 2 implica tener la puerta A que funciona como "Puerta bidireccional" para la transmisión y recepción de datos. Lo de bidireccional significa que funciona como puerta de entrada y salida, según se activen unas u otras líneas de control, sin necesidad de cambiar la programación de la puerta. Las figuras 8 y 9 muestra el diagrama funcional y el de tiempos del modo 2. La única puerta que funciona en este modo de operación es la puerta A, que utiliza cinco líneas de la puerta C como señales de control y status. En este modo, cada línea de la puerta A como entrada se comporta como un buffer latch igual que en el modo 1, y como salida también se comporta como un buffer latch triestate, a diferencia del modo 1 en que se comporta como un simple latch. El puerto B puede trabajar en modo 0 o 1 pero nunca en modo 2.

12

Figura 8 La puerta A en modo 2 se comporta como una verdadera puerta bidireccional diseñada para hacer de interfase entre dos microprocesadores o entre un microprocesador y un periférico el cual transmite y recibe datos. Por ejemplo, un disco flexible (flopy disc) podría ser interconectado a un microcomputador a través de una PPI en modo 2. Las líneas de control y status son las mismas que se utilizan en el modo 1. Cuando el puerto A funciona como entrada el comportamiento es similar al modo 1. Cuando funciona como salida además del latch tiene un buffer tri-state que se habilita cuando la señal ACK toma el valor "0". Las señales de control para la comunicación son: STB A: Señal de strobe de entrada. Carga los datos enviados por el periférico en el puerto A. Esta señal está presente en PC4. IBF A: Señal generada por el PPI en contestación a STB A indicando que se ha recibido el dato, con lo cual el periférico sabe que puede escribir un nuevo dato en la PPI. Esta señal se presenta en PC5. Las señales de control cuando los datos salen de la PPI son: OBF A: Señal de salida de la PPI que es generada cuando la CPU le escribe un dato en el puerto. Esta señal tiene por función indicarle al periférico que tiene un dato disponible para él. PC7 se encarga de esta señal.

13

ACK A: Señal de entrada a la PPI generada por el periférico indicándole a la PPI que se ha recibido el dato. Cuando esta señal está activa en "0" la salida abandona el tercer estado para presentar el dato que previamente escribió la CPU. Esta señal se presenta en PC6. INTR: Esta señal se encarga de pedirle interrupción a la CPU a través de PC3 cuando el periférico escribió un dato en la PPI o cuando el periférico leyó el dato enviado desde la CPU. Las interrupciones tienen una doble función: indicarle a la CPU cuando el periférico escribió un dato en la PPI y avisarle cuando el periférico tomó un dato enviado por la CPU para que de esta manera envíe un nuevo dato. El diagrama de tiempos del modo 2 aparece en la figira 9.

Figura 9 Interrupciones en el modo 2. A través de la línea PC3 se genera la señal de interrupción que puede ser habilitada por los flip-flops internos INTE 1 e INTE 2. Estos solo pueden ser activados por soft-ware escribiendo en el registro de control bit-set/reset del puerto C. El bit INTE 1 se ha de activar a través de la selección de PC6 en el formato bitset/reset, permitiendo de esta manera las interrupciones provocadas por la salida de datos del puerto A. Para el bit INTE 2 se ha de seleccionar el bit PC4 en el formato bit-set/reset para permitir de esta manera las interrupciones provocadas por la entrada de datos a la PPI. El puerto B puede también generar sus propias interrupciones como se vio en la descripción del modo 1. La figura 10 muestra la combinación lógica de los bits de habilitación de

14

interrupciones y de las líneas de control. Los pines del puerto C que no se utilizan en líneas de control (PC0,1,2) pueden ser utilizados como entrada o salida según se configure el puerto C.

Figura 10

15